Scalable Architecture Lab

Scalable Architecture Lab (SARCHLAB) is a research lab that runs under the Computer Science Department of William & Mary, under the supervision of Dr. Yifan Sun. SARCHLAB aims to develop scalable and efficient computer architectures by emphasizing the capabilities for human to understand the architecture and for the architecture to serve human.

Hiring

SArchLab has no plan of hiring new Ph.D. students, research interns, or undergraduate research assistants in Spring 2026, Fall 2026 and Spring 2027.

Research Topics

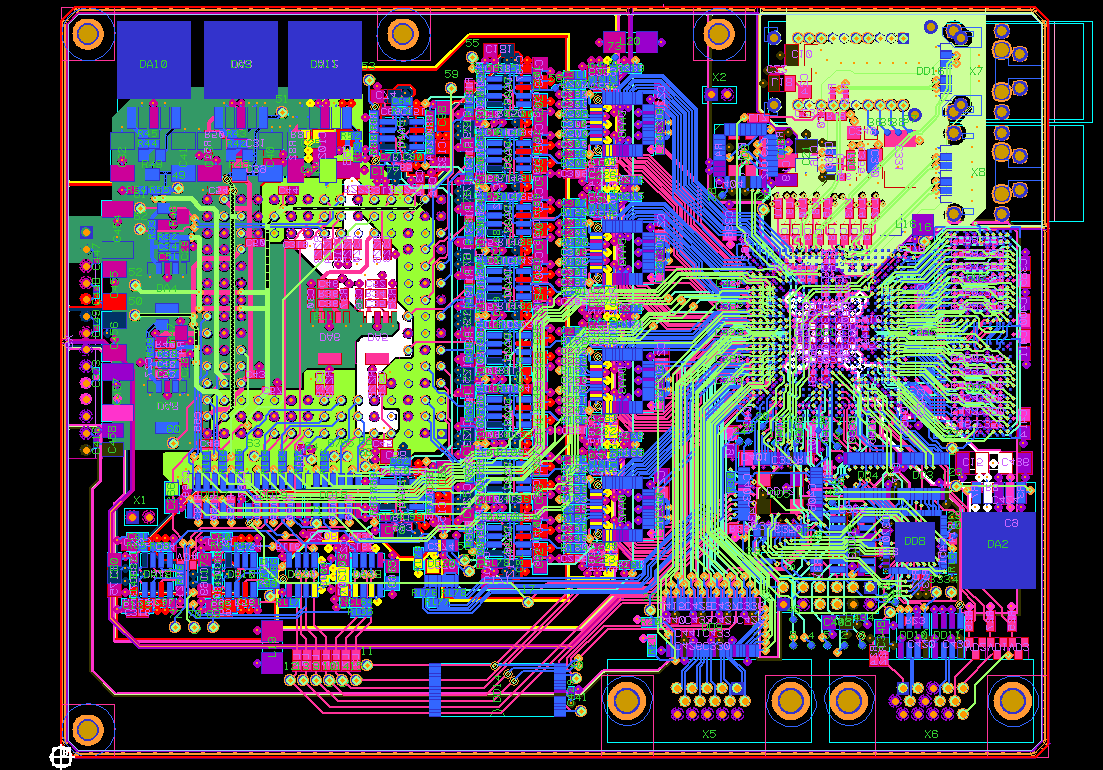

Explainable Architecture

Ever-increasing complex chip designs make them hard for humans to understand. If the designers cannot fully understand the architecture, the chip will inevitably contain hardware bugs, performance bottlenecks, reliability issues, and security vulnerabilities. Therefore, we need to develop data visualization tools that help designers make well-informed and evidence-based decisions.

Computer Architecture Simulation

A cycle-based simulator is an essential tool for computer architecture researchers to validate their ideas. The community requires the simulators to be easy to learn, highly flexible, highly performant, and highly accurate. I am honored to take the challenge and contribute to the community with the Akita simulator framework and the MGPUSim multi-GPU simulator.

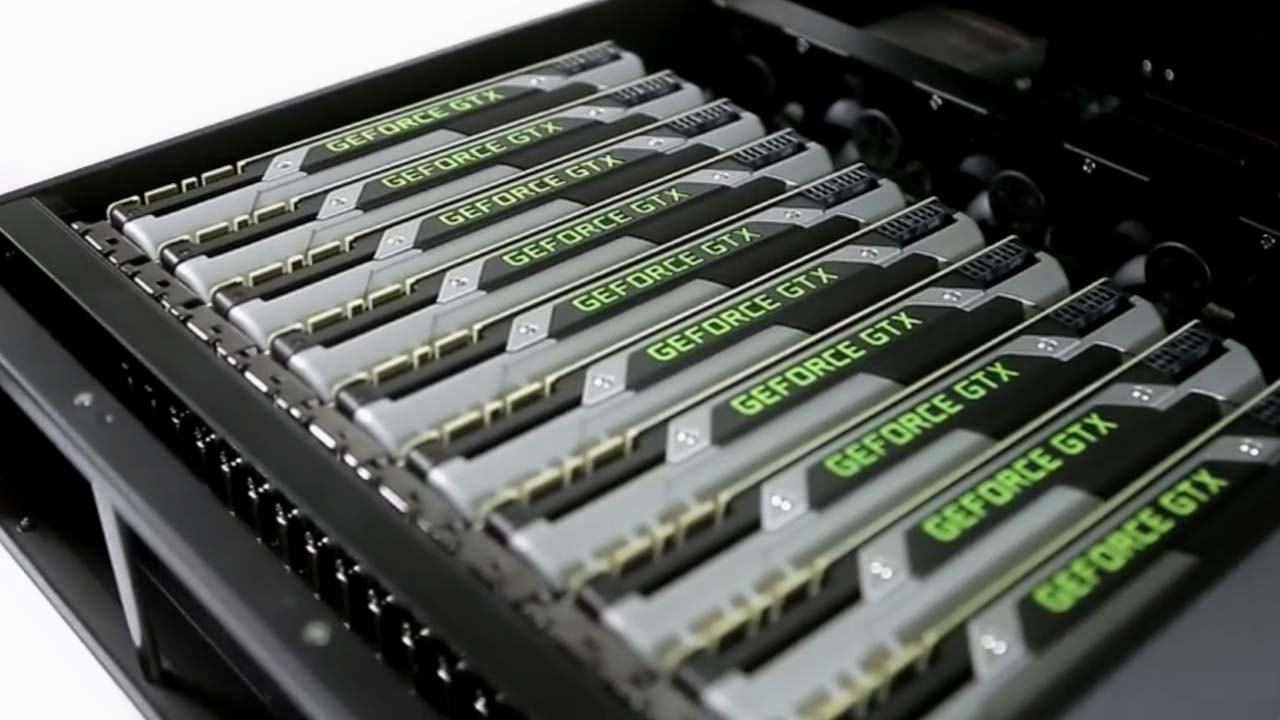

Multi-GPU and Wafer-Scale System Design

Single GPU systems struggle to meet the performance requirement. Therefore, researchers start to use large-scale multi-GPU systems to achieve extreme performance. Inter-GPU communication can easily kill the performance. I design architecture and system solutions for multi-GPU systems to avoid inter-GPU traffic and improve performance.

Sponsors

National Science Foundation

Advanced Micro Devices

Lab News

- [Mar 2026] Ying Li has received the W&M International Student Achievement Award! Congratulations Ying!

- [Jan 2026] Our paper "Designing AI Peers for Collaborative Mathematical Problem Solving with Middle School Students: A Participatory Design Study" has been accepted by CHI 2026! Congrats Wenhan!

- [Sep 2025] Our paper "HDPAT: Hierarchical Distributed Page Address Translation for Wafer-Scale GPUs" has been accepted by HPCA 2026! Congrats Daoxuan and Ying!

- [Sep 2025] Our paper "QuCo: Efficient and Flexible Hardware-Driven Automatic Configuration of Tile Transfers in GPUs" has been accepted by HPCA 2026! Thanks to our collaborators from NVIDIA and the University of Murcia.

- [Apr 2025] Our paper "Will Your Next Pair Programming Partner Be Human? An Empirical Evaluation of Generative AI as a Collaborative Teammate in a Semester-Long Classroom Setting" has been accepted by the 12th 2025 ACM Learning @ Scale Conference (L@S 2025)! Congrats Wenhan!

- [Mar 2025] Our paper "TrioSim: A Lightweight Simulator for Large-Scale DNN Workloads on Multi-GPU Systems" has been accepted by the 52nd International Symposium on Computer Architecture (ISCA 2025)! Congrats Ying!

- [Mar 2025] Two other papers have been accepted by ISCA 2025: "NetCrafter: Tailoring Network Traffic for Non-Uniform Bandwidth Multi-GPU Systems" and "The Sparsity-Aware LazyGPU Architecture". Thanks to our collaborators at UVA and NUS!

- [Mar 2025] Our paper "Luthier: A Dynamic Binary Instrumentation Framework Targeting AMD GPUs" has been accepted by ISPASS 2025. Daoxuan and Yuwei have been involved in this project. Thanks to our collaborators at Northeastern University!

- [Mar 2025] Our paper "Exploring the Wafer-Scale GPU" has been accepted by the GPGPU 2025 workshop and Daoxuan give a presentation at the workshop. Congrats Daoxuan!

- [Jan 2025] Daoxuan Xu has achieved Ph.D. candidacy. Congrats Daoxuan!

- [Jul 2024] Our paper "Looking into the Black Box: Monitoring Computer Architecture Simulations in Real-Time with AkitaRTM" has been accepted by the 57th IEEE/ACM International Symposium on Microarchitecture (MICRO '24')! Congrats Ali!

- [Apr 2024] Our paper "Evaluating the Effectiveness of LLMs in Introductory Computer Science Education: A Semester-Long Field Study" has been accepted by the Tenth ACM Conference on Learning @ Scale (L@S '24') !

- [Mar 2024] Our First Lightweight Community Workshop on Akita and MGPUSim has been successfully organized. Thank you all for participating in the event.

- [Jan 2024] Our paper "Impact of Raindrops on Camera-Based Detection in Software-Defined Vehicles" has been accepted by the 2nd IEEE International Conference on Mobility: Operations, Services, and Technologies (MOST '24') !

- [Jan 2024] Sabila Al Jannat has achieved Ph.D. candidacy. Congrats!

- [Nov 2023] Our paper "Visual Exploratory Analysis for Designing Large-Scale Network-on-Chip Architectures: A Domain Expert-Led Design Study" has been accepted by TVCG!

- [Sep 2023] Our paper "Path Forward Beyond Simulators: Fast and Accurate GPU Execution Time Prediction for DNN Workloads" has been accepted by MICRO 2023! Congrats Ying!

- [Sep 2023] Our paper "Photon: A Fine-grained Sampled Simulation Methodology for GPU Workloads" has been accepted by MICRO 2023!

- [Sep 2023] Daoxuan Xu has joined our lab as a Ph.D. student. Welcome!

- [Mar 2023] Our NSF CCRI Proposal Enabling Computer Architecture Simulation as a Service has been awarded! Thanks to NSF and my collaborator Kate Isaacs!

- [Feb 2023] Our NSF CRII Proposal Building Explainable Architecture with Simulation and Visualization Techniques has been awarded! Thank you NSF!

- [Dec 2022] Our book Accelerated Computing with HIP is published! It is available on Amazon or Barnes & Noble.

- [Aug 2022] Out CHIP dataset has been highlighted by the "Data Is Plural" column of FiveThirtyEight.